# A Class of 1-Bit Multi-Step Look-Ahead $\Sigma$ - $\Delta$ Modulators

Charis Basetas, Student Member, IEEE, Thanasis Orfanos, Student Member, IEEE, and Paul P. Sotiriadis, Senior Member, IEEE

Abstract-Digital Multi-Step Look-Ahead (MSLA) 1-bit  $\Sigma$ - $\Delta$  modulators are introduced. They improve upon the stability and noise shaping characteristics of conventional 1-bit  $\Sigma$ - $\Delta$ modulators by minimizing quantization error metrics of the current and future output samples. The mathematical model of the proposed MSLA modulators is analyzed. It is shown that the MSLA modulators are equivalent to a system of conventional  $\Sigma$ - $\Delta$  modulators in parallel, but with a common multi-input 1-bit quantizer instead of a typical one. The properties of this multiinput quantizer are studied and the transfer functions of the MSLA modulators are derived. Simulation results are presented demonstrating the advantages of the MSLA modulators over conventional 1-bit  $\Sigma$ - $\Delta$  ones in a number of applications. A parametric hardware architecture of the MSLA modulators is presented offering an adjustable trade-off between performance and hardware complexity based on the number of look-ahead steps. Finally, a FPGA implementation of a MSLA modulator is presented along with simulation results.

*Index Terms*—1-bit quantization, all-digital, DAC, look-ahead, modulator, noise shaping, optimization algorithm, sigma-delta.

#### I. INTRODUCTION

**THE** noise shaping characteristics and simplicity of  $\Sigma$ - $\Delta$  modulators have led to their widespread usage in high-resolution Digital-to-Analog Converters (DAC), Analogto-Digital Converters (ADC) and time-to-digital converters. Initially,  $\Sigma - \Delta$  modulators were designed as purely analog or mixed-signal circuits [1]. Because digital circuits are unaffected by process, voltage and temperature variations, and are becoming faster, more energy-efficient and smaller with the scaling of IC process technologies, there has been an increasing interest in all-digital  $\Sigma$ - $\Delta$  modulators [2]. These modulators are used as components in a variety of applications ranging from traditional data converters to all-digital transmitters [3], [4], frequency synthesizers [5], [6] and PLLs [7]. Moreover, a  $\Sigma$ - $\Delta$  DAC is the combination of an all-digital  $\Sigma$ - $\Delta$  modulator followed by a 1-bit or few-bit DAC, which is much easier to design than a multi-bit one.

Since  $\Sigma - \Delta$  modulation is based on a feedback loop, stability requirements are crucial for a successful design. These require-

Manuscript received January 28, 2016; revised April 25, 2016 and July 13, 2016; accepted August 19, 2016. Date of publication October 26, 2016; date of current version January 6, 2017. This work was partially supported by Broadcom Foundation USA. This paper was recommended by Associate Editor P. Rombouts.

The authors are with the National Technical University of Athens, Heroon Polytechniou 9, 15780 Zografou, Greece (e-mail: chbasetas@gmail.com; orfanos8@hotmail.com; pps@ieee.org).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TCSI.2016.2608922

ments pose restrictions to the noise transfer function (NTF) design space and limit the allowable input signal range [1], [8]. The quantizer resolution of the  $\Sigma$ - $\Delta$  modulator also affects its stability [9]. Single-bit modulators are more susceptible to instability than multi-bit ones, but the tendency towards DAC-less all-digital architectures necessitates the use of 1-bit  $\Sigma$ - $\Delta$  modulators. Furthermore, 1-bit quantization is inherently linear since there are only two signal levels and thus the matching requirements between different components are significantly relaxed.

Many works have dealt with the stability analysis of  $\Sigma$ - $\Delta$  modulators. Parallel decomposition of high-order modulators [10], limit cycle investigation [11] and quasi-linear modeling using the describing function method [12] are some of the proposed stability analysis techniques, while in [13] the stability of band-pass  $\Sigma$ - $\Delta$  modulators is considered.

This work proposes an all-digital Multi-Step Look-Ahead (MSLA) 1-bit modulation scheme which improves on the stability of conventional  $\Sigma$ - $\Delta$  modulators. This is achieved by taking into account future input samples for the determination of the current output. The number of look-ahead steps is a design parameter which is selected in order to obtain the desired balance between complexity and stability improvement. The enhanced stability offers more flexibility in the selection of the NTF, allowing for NTFs with increased pass-band bandwidth and out-of-band gain. This results in higher in-band noise attenuation and thus higher signal-tonoise-ratio (SNR).

In section II the process of 1-bit quantization is viewed as an optimization algorithm and the MSLA algorithm is introduced. The mathematical analysis of the MSLA modulator follows in section III, where its relation to conventional  $\Sigma$ - $\Delta$  and other look-ahead modulators is investigated. In section IV simulation results for a variety of applications are presented and the stability improvement offered by the MSLA modulator is quantified. Section V introduces a digital hardware architecture for the implementation of the MSLA modulator and a test-case FPGA implementation is presented. Finally, section VI concludes the discussion.

# II. 1-BIT QUANTIZATION AS AN OPTIMIZATION ALGORITHM

The process of 1-bit quantization is viewed as an optimization problem. The high resolution input sequence is passed through a band-selective filter. The filter is chosen to have a profile similar to the information spectrum of the input sequence. This maintains the information while pushing the

1549-8328 © 2016 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

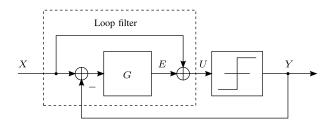

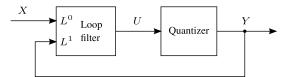

Fig. 1. The 1-bit error-feedback  $\Sigma$ - $\Delta$  modulator.

1-bit quantization error power outside the information spectrum minimizing the total in-band quantization error.

In [14] it is shown that the error-feedback  $\Sigma - \Delta$  modulator (EF SDM) produces a 1-bit output sequence with the minimum quantization error power when a first-order loop filter is used. This  $\Sigma - \Delta$  modulator forms the basis for the development of the MSLA modulator. In the following analysis it is shown that the EF SDM depicted in Fig. 1 may be viewed as an optimization algorithm. The MSLA modulator is then introduced as an extension of the EF SDM, where future input values are used as part of the optimization process.

For the reader's convenience, an overview of the notation used in this and the next sections is presented in Appendix A.

#### A. The 1-Bit Error-Feedback $\Sigma$ - $\Delta$ Modulator

From inspection of the system in Fig. 1 it is

$$U(z) = X(z) + G(z)(X(z) - Y(z))$$

(1)

where X(z), Y(z) and U(z) are the z-transforms of the input, output and quantizer input respectively and G(z) is the transfer function of filter G. The quantization error is N(z) = Y(z) - U(z), which combined with (1) and eliminating U(z) gives Y(z) = X(z) + 1/(1 + G(z))N(z). Thus, the signal and noise transfer functions are  $STF(z) \equiv$  $Y(z)/X(z)|_{N(z)=0} = 1$  and  $NTF(z) \equiv Y(z)/N(z)|_{X(z)=0} =$ 1/(1 + G(z)) respectively. A realizable EF SDM requires at least a single sample delay in filter G, which also translates to  $NTF(\infty) = 1$  [1]. So, the general form of G(z) is

$$G(z) = \frac{1 - NTF(z)}{NTF(z)} = \frac{\sum_{i=1}^{\ell} b_i z^{-i}}{1 + \sum_{i=1}^{m} a_i z^{-i}}$$

(2)

where  $\ell$ , *m* are the orders of the numerator and the denominator polynomials respectively. Filter *G* is also known as the comparison filter.

In [15] it is shown that the EF SDM is equivalent to an optimization algorithm and its output is determined by minimizing the cost function<sup>1</sup>

$$S_{0,n}(v) = |x_n + e_n - v|.$$

(3)

Here,  $x_n$  is the current input,  $e_n$  is the current comparison filter output and  $v \in \{\pm 1\}$  is the minimizing variable. The output  $y_n$  is the value of v minimizing the cost function  $S_{0,n}$ , i.e.

$$y_n = \underset{v \in \{\pm 1\}}{\arg\min} S_{0,n}(v).$$

(4)

<sup>1</sup>The first subscript 0 indicates that the cost function takes into account 0 look-ahead steps, while the second subscript n denotes that it is calculated at time index n.

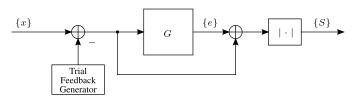

Fig. 2. Cost function calculation block diagram.

| Mir   | nimizi | ng va  | riables:      | v         |                  |                               |

|-------|--------|--------|---------------|-----------|------------------|-------------------------------|

| 0     | 1      |        | $n\!-\!2$     | n-1       | n                | Cost                          |

| $y_0$ | $y_1$  |        | $y_{n-2}$     | $y_{n-1}$ | -1               | $S_{0,n}(-1)$<br>$S_{0,n}(1)$ |

| $y_0$ | $y_1$  |        | $y_{n\!-\!2}$ | $y_{n-1}$ | 1                | $S_{0,n}(1)$                  |

|       | Pr     | evious | outputs       |           | Trial<br>FB seq. |                               |

Fig. 3. Overview of the EF SDM optimization algorithm.

The solution of (4) is  $y_n = \text{sgn}(e_n + x_n)$  and is implemented by the 1-bit quantizer in the EF SDM of Fig. 1. From (3) and (4) we note that the output of the 1-bit EF SDM is determined by minimizing *only* the *instantaneous* quantization error.

A block diagram of the cost function calculation of (3) is shown in Fig. 2. The negative feedback loop from the output to the input has been replaced by the trial feedback generator. At each iteration of the algorithm it generates all the possible values of v, namely -1 and 1 here. The quantization error which is the difference between the input sequence and the trial feedback generator sequence<sup>2</sup>, i.e.,  $(x_0 - y_0, x_1 - y_1, \ldots, x_{n-1} - y_{n-1}, x_n - v)$ , is filtered by 1 + G(z) = 1/NTF(z). The absolute value of the filter output is the cost function. The square of the cost function is thus equal to the filtered quantization error power.

The output selection procedure of the EF SDM by utilizing the optimization algorithm is illustrated in Fig. 3. The output sequence with the least cost is chosen and the corresponding  $y_n$  output value is appended to the output sequence. This process gives the same output sequence {y} as the 1-bit EF SDM with the same comparison filter G.

#### B. The MSLA Modulator Algorithm (k Look-Ahead Steps)

A generalization of the 1-bit quantization optimization problem is possible if the minimization of the filtered quantization error is not restricted to the current input sample  $x_n$ , but incorporates the next k future input samples as well, which are also called *look-ahead* samples. It should be noted that the future input samples are not in any way predicted; they are already available and the term "future" refers to a time delay of the output sequence by k samples.

The key idea is to "search" among all the  $2^{k+1}$  possible output sequences  $\{(v_0, v_1, \ldots, v_k) | v_i \in \{\pm 1\}\}$ , also known as *paths*. The MSLA algorithm assesses the  $2^{k+1}$  paths and selects the one with the minimum total quantization error power. Then, the first element of this path is selected as the

$<sup>^{2}</sup>$ Throughout the paper we assume zero initial conditions of the filters and all signals being zero for negative time index.

| Min  | . var.:   | $v_0$ |     | $v_{k-r}$   |        | $v_k$     |                                                                                         |                            |

|------|-----------|-------|-----|-------------|--------|-----------|-----------------------------------------------------------------------------------------|----------------------------|

|      | n-1       | n     |     | n+k-r       |        | $n\!+\!k$ | Cost                                                                                    | ]                          |

|      | $y_{n-1}$ | -1    |     | -1          |        | -1        | $D(\mathbf{v}_0)$                                                                       |                            |

|      | $y_{n-1}$ | -1    | ••• | $^{-1}$     |        | 1         | $D(\mathbf{v}_1)$                                                                       |                            |

| ÷    | ÷         | ÷     | ÷   | ÷           | ÷      | :         | :                                                                                       | $\left  \right ^{2^{k+1}}$ |

|      | $y_{n-1}$ | 1     |     | 1           |        | $^{-1}$   | $D(\mathbf{v}_{2^{k+1}-2})$                                                             |                            |

|      | $y_{n-1}$ | 1     |     | 1           |        | 1         | $ \begin{array}{c} D(\mathbf{v}_{2^{k+1}-2}) \\ D(\mathbf{v}_{2^{k+1}-1}) \end{array} $ | J                          |

| Prev | . Out.    |       |     |             | r+1    |           |                                                                                         |                            |

|      |           | k     | + 1 | trial feedb | ack sy | mbols     |                                                                                         |                            |

Fig. 4. Overview of the MSLA optimization algorithm.

current output. Finally, time index *n* is increased by one and the algorithm proceeds. This process is captured in Fig. 2 where the feedback generator outputs the  $2^{k+1}$  possible paths generating the input to comparison filter *G*:

$$(x_0 - y_0, x_1 - y_1, \dots, x_{n-1} - y_{n-1}, x_n - v_0, x_{n+1} - v_1, \dots, x_{n+k} - v_k).$$

(5)

The associated costs are  $\sum_{j=0}^{k} S_{j,n}(v_0, v_1, ..., v_j)$ , where the *partial costs*  $S_{j,n}$  are defined as

$$S_{j,n}(v_0, v_1, \dots, v_j) = |x_{n+j} + e_{n+j} - v_j|^2.$$

(6)

Extensive simulation suggests that taking into account only the partial costs associated with the last few look-ahead samples, i.e., j = k - r, k - r + 1, ..., k, as shown in Fig. 4, may result in superior stability and lower complexity at the cost of reduced SNR. In this case, the total cost of a path is given by (7) where we have set  $\mathbf{v} = (v_0, v_1, ..., v_k)$ .

$$D_n(\mathbf{v}) = \sum_{j=k-r}^k S_{j,n}(v_0, v_1, \dots, v_j)$$

(7)

The MSLA modulator output is the value of  $v_0$ , which along with the values of  $v_1, v_2, ..., v_k$  minimize  $D_n(\mathbf{v})$ , i.e.,

$$y_n = \arg\min_{v_0 \in \{\pm 1\}} \left( \min_{v_1, v_2, \dots, v_k \in \{\pm 1\}} D_n(\mathbf{v}) \right).$$

(8)

Since filter G in Fig. 2 is in general an infinite impulse response (IIR) one, and thus its output depends on all previous and current input samples, the comparison filter output  $e_{n+j}$  is an implicit function of  $v_0, v_1, \ldots, v_{j-1}$ . Assuming G is as in (2) and since its input is given by (5), its output for  $0 \le j \le k$  is

$$e_{n+j} = \sum_{i=1}^{\ell} b_i x_{n+j-i} - \sum_{i=1}^{j} b_i v_{j-i} - \sum_{i=j+1}^{\ell} b_i y_{n+j-i} - \sum_{i=1}^{m} a_i e_{n+j-i}$$

(9)

Instead of using the square of the absolute value for the partial cost in (6), an alternative is to use the absolute value. In this case the output of the MSLA modulator is given again by (8) and (7), but (6) is replaced by

$$S_{j,n}(v_0, v_1, \dots, v_j) = |x_{n+j} + e_{n+j} - v_j|.$$

(10)

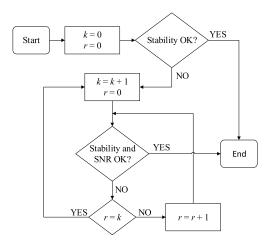

Fig. 5. r, k selection flowchart.

Using the absolute value can result in more efficient quantizer designs as it is shown later. Because of this, the focus of our analysis considers partial costs as in (10). Moreover, simulation results in subsequent sections indicate that the output spectrum does not depend significantly on either choice.

The number of partial costs used in (7) is determined by r and reflects to the complexity of the modulator. The choice of look-ahead steps k and r for a given filter G, and therefore a given NTF and STF, can be made as shown in Fig. 5.

The assessment of stability is done via simulation as with a conventional  $\Sigma$ - $\Delta$  modulator. This is because of the lack, to our knowledge, of an accurate theoretical model predicting stability in look-ahead modulators. A range of simulation runs with varying DC and sinusoidal input amplitudes and frequencies is typically used to provide a trustworthy estimate. The reader is referred to [1, Chapter 8] for details on the simulation procedure.

#### C. The Optimal Solution to the 1-Bit Quantization Problem

Let us consider the case of an input sequence of finite yet arbitrary length N. Then the optimal solution to the 1-bit quantization optimization problem in terms of SNR is obtained by solving the minimization problem

$$(y_0, y_1, \dots, y_{N-1}) = \underset{v_0, v_1, \dots, v_{N-1} \in \{\pm 1\}}{\operatorname{arg\,min}} D_n(\mathbf{v})$$

(11)

where  $D_n(\mathbf{v}) = \sum_{j=0}^{N-1} |x_j + e_j - v_j|^2$ . In this case the trial feedback generator of Fig. 2 outputs all the 2<sup>N</sup> possible trial sequences just like the MSLA modulator. However, this time, the whole trial feedback sequence  $(v_0, v_1, \dots, v_{N-1})$  resulting in the minimum total quantization power is chosen as the output sequence  $(y_0, y_1, \dots, y_{N-1})$ .

A more efficient solution to the aforementioned problem is Viterbi decoding [14], [16]. However, Viterbi decoding is only possible for filters G with a finite state machine representation, which rules out most IIR filters G with poles on the unit circle such as the ones based on a  $\Sigma$ - $\Delta$  modulator NTF. Note that the complexity of both approaches is prohibiting for input signals with a significant length, while they are inapplicable to realtime streaming signals. Reduced complexity techniques such

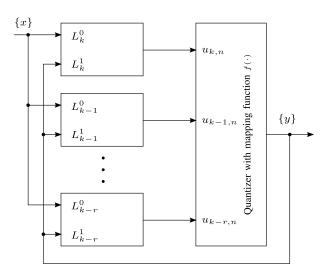

Fig. 6. The MSLA modulator efficient form system diagram.

as list decoding or M-algorithm [17] have been introduced, but their complexity remains too high. Therefore, even lower complexity look-ahead algorithms are needed, such as the MSLA.

#### **III. MSLA MODULATOR EFFICIENT FORM**

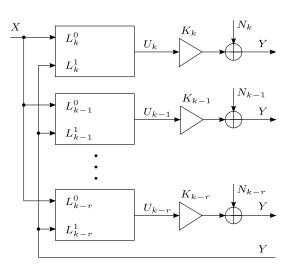

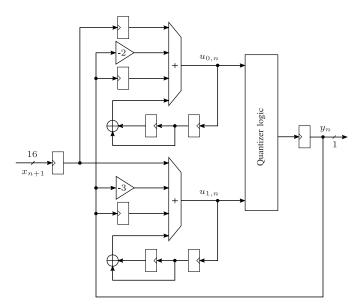

Brute force solution of the MSLA optimization problem in (8) via (7) and (10) requires the computation of  $2^{k+1}$ cost values in every time step. Note also that the total cost function  $D_n$  depends on time n. A more efficient approach instead is to convert the optimization-form of the MSLA modulator into the equivalent nonlinear feedback system form in Fig. 6. The system is comprised of r + 1 two-input filters and a multivariable nonlinear function  $f(\cdot) : \Re^{r+1} \to {\pm 1}$ . Function f can be considered as the equivalent to the 1-bit quantizer of the conventional  $\Sigma$ - $\Delta$  modulator.

Following some algebraic manipulation in Appendix B an equivalent expression of (10) for  $k - r \le j \le k$  is

$$S_{j,n}(v_0, v_1, \dots, v_j) = \left| u_{j,n} - \sum_{i=0}^j c_{j,i} v_{j-i} \right|$$

(12)

which is a function of a linear combination of  $v_0, v_1, ..., v_j$ , parameterized on  $u_{j,n}$ , where

$$u_{j,n} = \sum_{i=0}^{j} c_{j,i} x_{n+j-i} + \sum_{i=j+1}^{j+\ell-1} c_{j,i} \left( x_{n+j-i} - y_{n+j-i} \right) + \sum_{i=0}^{m-1} d_{j,i} e_{n-i}.$$

(13)

Constant coefficients  $c_{j,i}$  and  $d_{j,i}$  result from the comparison filter *G* and are derived in Appendix B. Also note that  $u_{j,n}$  is independent of  $v_0, v_1, ..., v_j$ . For the special case of j = 0,  $u_{0,n} = x_n + e_n$  and  $S_{0,n}(v_0) = |u_{0,n} - v_0|$ .

Substituting (12) into (7) and using (8) gives the following expression for the MSLA modulator output

$$y_n = f(u_{k-r,n}, u_{k-r+1,n}, \dots, u_{k,n})$$

(14)

Fig. 7. The general  $\Sigma$ - $\Delta$  modulator system diagram.

where function f is defined as the solution of the timeinvariant (i.e., f does *not* depend on n) combinatorial problem

$$f\left(u_{k-r,n}, u_{k-r+1,n}, \dots, u_{k,n}\right) = \arg\min_{v_0 \in \{\pm 1\}} \left( \min_{\substack{v_1, v_2, \dots, v_k \\ \in \{\pm 1\}}} \sum_{j=k-r}^{k} \left| u_{j,n} - \sum_{i=0}^{j} c_{j,i} v_{j-i} \right| \right).$$

(15)

This equation forms the foundation of the proposed methodology. The behavior of function  $f(\cdot)$  is investigated in Section III-B.

Having function f we now derive filters  $L_j^{0,1}(z)$ ,  $k - r \le j \le k$  to complete the MSLA modulator equivalent in Fig. 6. For j = 0 (9) gives  $e_n = \sum_{i=1}^{\ell} b_i (x_{n-i} - y_{n-i}) - \sum_{i=1}^{m} a_i e_{n-i}$ . Its z-transform is

$$E(z) = G(z) \left( X(z) - Y(z) \right)$$

(16)

where G(z) is defined in (2).

Taking the z-transform of (13) with respect to n and combining it with (16) yields

$$U_j(z) = L_j^0(z)X(z) + L_j^1(z)Y(z)$$

(17)

where  $U_j(z)$  is the *z*-transform of the *j*-th filter output (Fig. 6) and

$$L_{j}^{0}(z) = \sum_{i=0}^{j+\ell-1} c_{j,i} z^{j-i} + G(z) \sum_{i=0}^{m-1} d_{j,i} z^{-i}$$

(18)

$$L_j^1(z) = -\sum_{i=j+1}^{j+\ell-1} c_{j,i} z^{j-i} - G(z) \sum_{i=0}^{m-1} d_{j,i} z^{-i}$$

(19)

with  $k - r \leq j \leq k$ .

Equations (14) and (17) establish the equivalence of the MSLA modulator system in Fig. 6 with that in Fig. 2. The form in Fig. 6 may be considered as an extension of the general  $\Sigma$ - $\Delta$  modulator system shown in Fig. 7 [1].

#### A. MSLA Modulator Transfer Functions

As a first-order approximation, the multi-input quantizer function f in Fig. 6 is replaced by r + 1 correlated additive noise sources and loop gains  $K_j$ ,  $k - r \le j \le k$  as shown in Fig. 8. In the r + 1 resulting loops the noise sources are such that added to their corresponding filter output produce the same output y. This means that the transfer functions may be derived using any of the r + 1 simple loops.

To proceed we choose to define the NTF based on the first (top) of the r + 1 loops. The reasoning for this is that the first filter  $(L_k^0, L_k^1)$  incorporates the highest look-ahead order and therefore captures most of the MSLA modulator dynamics.

Fig. 8. The MSLA modulator efficient form system diagram with the quantizer replaced by noise sources.

To derive the NTF we set X(z) = 0 and we define  $N_k(z)$  as the *z*-transform of the noise source added to the filter output  $K_k U_k(z)$ . Then

$$Y(z) = N_k + K_k L_k^1(z) Y(z).$$

(20)

So, the NTF is

$$NTF_{\text{MSLA}} \equiv \left. \frac{Y}{N_k} \right|_{X=0} = \frac{1}{1 - K_k L_k^1}.$$

(21)

The STF is

$$STF_{\text{MSLA}} \equiv \left. \frac{Y}{X} \right|_{N_i=0} = \frac{K_k L_k^0}{1 - K_k L_k^1}.$$

(22)

Following the analysis in [1, Section 2.1],  $K_k$  is calculated by minimizing the average power of the quantizer's linear model error  $y_n - K_k u_{k,n}$ . This leads to

$$K_{k} = \frac{\langle y, u_{k} \rangle}{\langle u_{k}, u_{k} \rangle} = \frac{\langle f(\mathbf{u}), u_{k} \rangle}{\sigma_{u_{k}}^{2}}$$

(23)

where  $\langle a, b \rangle$  is defined either stochastically as E[ab] or deterministically as the time average  $\lim_{N\to\infty} \frac{1}{N} \sum_{n=0}^{N} a_n b_n$ of the sequences  $a_n$  and  $b_n$ . The impact of the other loop filters is included in the quantizer gain  $K_k$ , and therefore in the NTF and STF, via the inner product of  $f(\mathbf{u})$  with  $u_k$ . The value of  $K_k$  can be derived via simulation. The expressions for the NTF and STF of the MSLA modulator are comparable to the ones obtained for the conventional  $\Sigma$ - $\Delta$  modulator depicted in Fig. 7 [1].

To avoid confusion, please note that in the remainder of the paper the NTF of the MSLA modulator is denoted as  $NTF_{MSLA}$ . The notation NTF is reserved for the initial EF SDM NTF used as the basis for the MSLA modulator comparison filter G defined in (2).

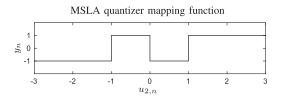

Fig. 9. The MSLA modulator quantizer function f for  $NTF = (1 - 2\cos(2\pi \cdot 0.365)z^{-1} + z^{-2})^2$ , k = 2 and r = 0.

#### B. MSLA Modulator Quantizer Aspects

An alternative expression for the MSLA modulator quantizer function  $f(\cdot)$  can be derived by defining

$$\tilde{D}(\mathbf{u}, \mathbf{v}) = \sum_{j=k-r}^{k} \left| u_{j,n} - \sum_{i=0}^{j} c_{j,i} v_{j-i} \right|$$

(24)

where  $\mathbf{u} = (u_{k-r,n}, u_{k-r+1,n}, \dots, u_{k,n})$  and  $\mathbf{v} = (v_0, v_1, \dots, v_k)$ . Since the output of the modulator is determined solely by the value of  $v_0$  (see (15)), we can distinguish between two sets of values of  $\tilde{D}(\mathbf{u}, \mathbf{v})$ , i.e.,

$$A(\mathbf{u}) = \{ D(\mathbf{u}, \mathbf{v}) : \mathbf{v} = (1, v_1, v_2, ..., v_k) \mid v_i \in \{\pm 1\} \} \text{ and } B(\mathbf{u}) = \{ \tilde{D}(\mathbf{u}, \mathbf{v}) : \mathbf{v} = (-1, v_1, v_2, ..., v_k) \mid v_i \in \{\pm 1\} \}$$

with each set containing  $2^k$  elements. Given the input vector **u**, the modulator output is

$$f(\mathbf{u}) = \begin{cases} 1 & \text{if } \min A(\mathbf{u}) \le \min B(\mathbf{u}) \\ -1 & \text{otherwise.} \end{cases}$$

(25)

Thus, the domain space  $\Re^{r+1}$  of f is partitioned into the two subsets  $f^{-1}(\{+1\})$  and  $f^{-1}(\{-1\})$ . Note that the minimization process is independent of time index n and thus f is a static function.

The following examples illustrate the form of f as given by (25) for different NTFs and values of k and r:

*Example 1:* The quantizer function  $f(\cdot)$  of a MSLA modulator with  $NTF = (1 - 2\cos(2\pi \cdot 0.365)z^{-1} + z^{-2})^2$ , k = 2 and r = 0 is

$$f(u_{2,n}) = \begin{cases} 1, & u_{2,n} \in [-1,0) \cup [1,\infty) \\ -1, & u_{2,n} \in (-\infty,-1) \cup [0,1). \end{cases}$$

(26)

It can also be expressed using signum functions as

$$f(u_{2,n}) = \text{sgn} (u_{2,n} + 1) \cdot \text{sgn} (u_{2,n}) \cdot \text{sgn} (u_{2,n} - 1).$$

(27)

In this case, the effect of the MSLA modulator is the inversion of the quantizer output in the interval [-1, 1] compared to a conventional  $\Sigma$ - $\Delta$  modulator 1-bit quantizer (Fig. 9).

*Example 2:* Let  $NTF = (1 - z^{-1})^3$ , k = 2 and r = 0. The resulting quantizer function is the same as that of a conventional  $\Sigma$ - $\Delta$  quantizer, i.e.,  $f(u_{2,n}) = \text{sgn}(u_{2,n})$ . This is generally true in the case that  $|c_{k,k}| > \sum_{i=0}^{k-1} |c_{k,i}|$  and r = 0. *Example 3:* The previous examples dealt only with r = 0, so  $y_n$  was a function of  $u_{k,n}$  only. If r = 1, then  $y_n =$

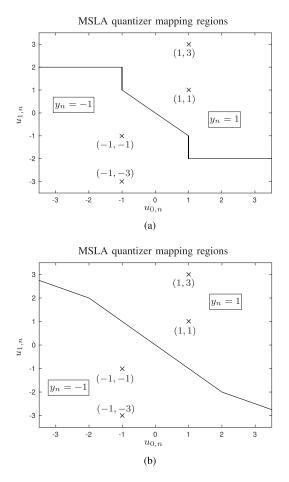

so  $y_n$  was a function of  $u_{k,n}$  only. If r = 1, then  $y_n = f(u_{k-1,n}, u_{k,n})$  and the mapping from  $\mathbf{u} = (u_{k-1,n}, u_{k,n})$  to  $y_n$  is formed by regions on a plane. This is seen in Fig. 10(a),

Fig. 10. Mapping regions from  $u_{0,n}$ ,  $u_{1,n}$  to  $y_n$  for the MSLA modulator with  $NTF = (1 - z^{-1})^2$ , k = 1, r = 1 and a total cost function employing (a) Manhattan or (b) Euclidean distance.

where the MSLA modulator is configured with  $(1 - z^{-1})^2$  as the comparison filter NTF, k = 1 and r = 1.

Fig. 10(a) depicts a Voronoi diagram [18] in two-dimensional space. The output of the modulator is determined by the least Manhattan distance of the quantizer input vector **u** from a set of points which depend on the coefficients  $c_{j,i}$ . These points are also shown in Fig. 10(a). The coordinates of these points in  $u_j$  axes are given by  $\sum_{i=0}^{j} c_{j,i}v_{j-i}$  for all possible values of  $\mathbf{v} = (v_0, v_1, \dots, v_k)$ , resulting in a total of  $2^{k+1}$  points in (r + 1)-dimensional space.

*Example 4:* In the previous example, if Euclidean distance is used, i.e.,  $S_{j,n}$  are given by (6) instead of (10), the corresponding Voronoi diagram is shown in Fig. 10(b). In this case the output of the modulator is determined by the least Euclidean distance of the quantizer input vector **u** from the same set of points as in the previous example.

Voronoi diagrams employing Manhattan distance, and thus the corresponding MSLA modulator quantizer mapping regions, consist only of horizontal, vertical and  $\pm 45^{\circ}$  dividing lines (planes) [18]. The dividing lines (planes) of Euclidean distance Voronoi diagrams on the other hand are not subject to this restriction. The hardware implementation of the MSLA quantizer is either based on a LUT or on a number of comparisons involving its inputs. So, apart from some special cases,

TABLE I 1-bit Look-Ahead Σ -Δ Complexity Comparison

| Description                                                    | Filter<br>output calc. | Memory                      | Other                                             |

|----------------------------------------------------------------|------------------------|-----------------------------|---------------------------------------------------|

| Full LA                                                        | $N \cdot 2^N$          | _                           | Select min.                                       |

| LA with<br>re-use of results                                   | $2^{N+1}-2$            | $2^{N} - 1$                 | Select min.                                       |

| LA with select & cont.                                         | $2^N$                  | $2^N$                       | Select min.                                       |

| LA with<br>linear decomp.                                      | $2^{N-1}$              | $2^N$                       | Select min.                                       |

| Basic<br>pruned LA                                             | $N \cdot 2^N$          | $N \cdot L$                 | Path sorting                                      |

| Pruned LA with<br>re-use of results                            | $2^{N+1}-2$            | $N\!\cdot\!L\!+\!2^N\!-\!1$ | Path sorting                                      |

| Efficient trellis $\Sigma$ - $\Delta$ modulation               | $2 \cdot M$            | $M \cdot L$                 | Uniqueness of<br>last N symbols<br>+ path sorting |

| Pruned tree<br>$\Sigma$ - $\Delta$ modulation<br>(M-algorithm) | $2 \cdot M$            | $M \cdot L$                 | Path sorting                                      |

| MSLA $\Sigma$ - $\Delta$ modulation                            | $r\!+\!1$              | _                           | (r+1)-input 1-bit<br>quantizer logic              |

using the Manhattan distance results in a simpler hardware implementation of the quantizer. This is another reason why this work deals mostly with the Manhattan distance case.

As a test-case, the mapping functions of Fig. 10 were synthesized for a Xilinx Kintex-7 target device assuming two 7-bit inputs. After logical optimization the Manhattan distance quantizer was comprised of one 5-input LUT, three 6-input LUTs and one D flip-flop, whereas the Euclidean distance one had in addition one 3-input LUT, one 6-input LUT and one 2:1 multiplexer. The difference in hardware complexity becomes even more pronounced as the bit width or the number of quantizer inputs is increased.

In the previous examples we considered only r = 0 or r = 1. The results are similar when r > 1, but the mapping regions are formed in a (r + 1)-dimensional space and are not convenient for demonstration.

#### C. Complexity Comparison

In the previous sections it was shown that the MSLA modulator is composed of r+1 loop filters and an (r+1)-input quantizer. This setup offers significantly lower computational complexity than other look-ahead  $\Sigma$ - $\Delta$  implementations. Table I summarizes the complexity of a variety of look-ahead algorithms. These results are not bound to any specific hardware implementation, but they are based on the computational complexity of each algorithm. All of these algorithms are discussed thoroughly in [19], while the M-algorithm is also used in [17]. The first four algorithms of Table I are based on the full-look ahead algorithm.

The full look-ahead algorithm is derived from the MSLA one if we use Euclidean distance and let r = k = N, where N is the number of look-ahead samples. As it can be seen in the first four rows of Table I its complexity remains exponential and therefore its use becomes prohibiting for large values of N. Typical values are N = 10.

|      | n-1       | n    |       | n+L-N           |                 | $n\!+\!L\!-\!1$ | Cost                                                                          |    |

|------|-----------|------|-------|-----------------|-----------------|-----------------|-------------------------------------------------------------------------------|----|

|      | $y_{n-1}$ | 1    |       | -1              |                 | -1              | $D(\mathbf{v}_0)$                                                             |    |

|      | $y_{n-1}$ | 1    | • • • | -1              |                 | 1               | $D(\mathbf{v}_1)$                                                             |    |

| :    | ÷         | ÷    | ÷     | ÷               | ÷               | ÷               | ÷                                                                             | 2M |

|      | $y_{n-1}$ | 1    |       | 1               |                 | $^{-1}$         | $D(\mathbf{v}_{2M-2})$                                                        |    |

|      | $y_{n-1}$ | 1    |       | 1               |                 | 1               | $ \begin{array}{c} D(\mathbf{v}_{2M-2}) \\ D(\mathbf{v}_{2M-1}) \end{array} $ | J  |

| Prev | . Out.    | Same |       |                 | $\widetilde{N}$ |                 |                                                                               |    |

|      |           | -    |       | $\widetilde{L}$ |                 |                 |                                                                               |    |

Fig. 11. Overview of the M-algorithm optimization algorithm.

Reduced complexity techniques such as list decoding or M-algorithm [17] have been suggested for use in all-digital transmitters. M-algorithm does not assess  $2^{k+1}$  paths of length k + 1, as is the case with the full look-ahead and the MSLA algorithms. Instead, there are 2M paths of length L under investigation, with the restriction that their last  $N = \log_2(2M)$  symbols are different. Fig. 11 illustrates this approach.

At each iteration the M paths with the highest cost are discarded and 2M new paths are generated by appending either -1 or 1 to the remaining M paths. The cost associated with each path is  $D_n(\mathbf{v}_i) = \sum_{j=0}^{L} |x_{n+j} + e_{n+j} - v_j|^2$ . L should be sufficiently large so that all path samples at time index n are identical and their value is passed to the output. This is another significant difference between the MSLA and the M-algorithm. Typical values of the parameters are M = 16 and L = 1500. Moreover, the path updating process poses a significant overhead. Therefore the M-algorithm remains too complex for real-time signal conversion. In [20] it was proposed that the precalculated optimal output sequences for a given symbol are stored and then they are played-back during transmission to address hardware realization issues.

Assuming a typical value of r = 8, the reduction of complexity offered by the MSLA modulator is substantial, while its performance is comparable to that of the other implementations. The only overhead apart from the r + 1 loop filter output calculations, is the realization of the (r + 1)-input quantizer. A LUT approach is possible for moderate values of r, offering minimal delay at the cost of increased area. On the other hand a comparator-based approach would require less area at the cost of increased delay. The latter solution would require approximately the same resources as the path sorting algorithm needed by the other reduced complexity implementations.

#### D. Stability Analysis Considerations

A critical aspect of all 1-bit  $\Sigma$ - $\Delta$  modulators is their stability and stability limits. Because of their strongly nonlinear nature, the notion of stability relates to their desirable performance, and can accept a variety of definitions depending on the application and the mathematical tools used to analyze it. Simulations indicate that it is appropriate to treat the 1-bit  $\Sigma$ - $\Delta$  modulators as nonlinear dynamical systems and adopt the classical Describing-Function methodology using a quasilinear model of the quantizer, as it was presented in [12].

Using the methodology developed in [12], the stability limits of the MSLA modulator can be analyzed, but such an analysis is beyond the scope of this manuscript. Instead,

TABLE II Noise Transfer Functions of Fig. 12

|       | Transfer function                                                                                                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NTF 1 | $\frac{1\!-\!3.99646z^{-1}\!+\!5.993z^{-2}\!-\!3.99646z^{-3}\!+\!1.000000433z^{-4}}{1\!-\!3.131z^{-1}\!+\!3.7237z^{-2}\!-\!1.99z^{-3}\!+\!0.4029z^{-4}\!+\!3.5\cdot\!10^{-5}z^{-5}}$ |

| NTF 2 | $\frac{(1\!-\!z^{-1})(1\!-\!1.994z^{-1}\!+\!z^{-2})}{(1\!-\!0.5995z^{-1})(1\!-\!1.384z^{-1}\!+\!0.5892z^{-2})}$                                                                      |

| NTF 3 | $\frac{(1-z^{-1})(1-2z^{-1}+z^{-2})}{(1-0.6694z^{-1})(1-1.531z^{-1}+0.6639z^{-2})}$                                                                                                  |

| NTF 4 | $(1-z^{-1})^3$                                                                                                                                                                       |

| NTF 5 | $(1 - 2\cos(2\pi \cdot 0.365)z^{-1} + z^{-2})^2$                                                                                                                                     |

we have relied on a large number of simulations in order to illustrate the stability limits. The results are presented in the next section.

# **IV. SIMULATION RESULTS**

In the following subsections NTF is defined based on the transfer function G(z) as in (2), i.e., NTF(z) = 1/(1 + G(z)). It should be distinguished from  $NTF_{MSLA}$  given in (21).

#### A. The Effect of Look-Ahead Steps in Stability

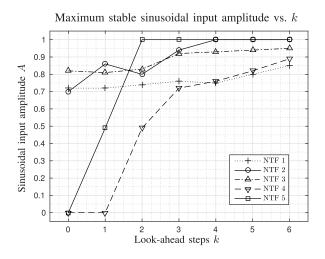

Simulation of several different comparison filters and associated NTFs indicates the stability improvement of the modulator as the number of look-ahead steps k is increasing. In the following comparative simulation results, the maximum sinusoidal input amplitude resulting in stable operation is chosen as the stability measure. Manhattan distances are used for the simulations.

Two kinds of NTFs were chosen; NTFs resulting in stable conventional  $\Sigma$ - $\Delta$  modulators and NTFs resulting in unstable ones. The selection of stable NTFs (NTFs 1-3 in Table II) was based on design guidelines in [1], [21], [22]. The unstable NTFs (4-5 in Table II) have their zeros on the unit circle with poles at z = 0. Typically NTFs stable in conventional  $\Sigma$ - $\Delta$ modulators are also stable in MSLA ones. Moreover, as k is increased they remain stable for higher input amplitudes, while unstable NTFs in conventional  $\Sigma$ - $\Delta$  modulators may become stable. The main advantage of resorting to a look-ahead  $\Sigma$ - $\Delta$ modulator instead of a conventional one is the possibility to use more aggressive NTFs in terms of out-of-band gain and thus achieve higher in-band noise attenuation and SNDR (Signal-to-Noise and Distortion Ratio).

The attained stability simulation results are shown in Fig. 12 and the corresponding filters are shown in Table II. The MATLAB simulation uses  $2 \cdot 10^6$  input samples. For the low-pass filters  $1-4 x_n = A \sin (2\pi \cdot 0.0041482n)$  was used as the input and for the band-pass filter 5 it was  $x_n =$  $A \sin (2\pi \cdot 0.365n)$ . The effect of the look-ahead steps k in increasing the maximum sinusoidal input amplitude for stable operation is evident. Especially, NTFs 4 and 5, unstable when used in a conventional  $\Sigma$ - $\Delta$  modulator loop, i.e., k = 0, result in stable operation for  $k \ge 1$  and  $k \ge 2$  respectively.

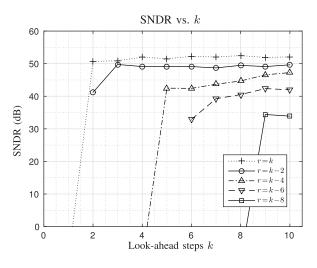

In Fig. 13 more simulation results for NTF 5 are presented, demonstrating the impact of k and r on the SNDR (Signal-to-Noise and Distortion Ratio). Here, the input is fixed to

Fig. 12. Maximum stable sinusoidal input amplitude for the Manhattan distance MSLA modulator with different look-ahead steps k and NTFs (shown in Table II). Various values for r are used.

Fig. 13. SNDR vs. look-ahead steps k for NTF 5 with r as a parameter.

$x_n = 0.4 \sin (2\pi \cdot 0.365n)$  and OSR = 64 is used for the calculation of the SNDR. The low OSR value is responsible for the relatively low SNDR values. The SNDR is in general increasing with k, while reducing the value of r from its maximum value of r = k results in less hardware complexity, but with a SNDR penalty. The results are similar for other loop filter selections. For the case of r = 0 it should be noted that the MSLA modulator is reduced to a conventional  $\Sigma$ - $\Delta$  one with a modified loop filter transfer function given by (18) and (19). As it can be seen in Fig. 13, in many cases this loop filter transformation results in stable loop filter transfer functions derived from NTF 5, which is unstable when used in a conventional  $\Sigma$ - $\Delta$  modulator.

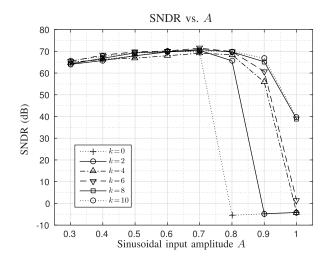

The performance of the MSLA modulator for NTF 2 in terms of SNDR vs. sinusoidal input amplitude A with k as a parameter and r = k is depicted in Fig. 14. The input is  $x_n = A \sin (2\pi \cdot 0.0041482n)$  and OSR = 32 is used for the calculation of the SNDR. As expected, the performance and stability are enhanced as the value of k is increased. Similar results are obtained for different comparison filters.

Fig. 14. SNDR vs. sinusoidal input amplitude A for NTF 2 with k as a parameter and r = k.

The first consideration for the selection of the NTF poles in a conventional  $\Sigma$ - $\Delta$  modulator is its stability. NTFs 4-5 have no poles for the reduction of the out-of-band gain and are unstable when used in a conventional  $\Sigma$ - $\Delta$  modulator [1]. The obtained simulation results demonstrate that such NTFs used in a MSLA modulator can offer stable operation for a wide range of input amplitudes provided that k is sufficiently large ( $\geq 2$ ). Thus, the design space of the NTF is greatly increased allowing for the selection of the zeros and poles of the NTF based on other design criteria apart from stability. One such criterion is the possibility to have convenient filter coefficients such as powers of 2 (or a sum of two or three of them). This filter coefficient selection reduces multiplications and thus increases the speed and the efficiency of the MSLA modulator, leading also to less chip area compared to a MSLA modulator with a loop filter requiring a significant amount of multiplications.

In conclusion, the MSLA modulator offers higher input dynamic range than a conventional  $\Sigma$ - $\Delta$  modulator with the same NTF. Furthermore, a more aggressive NTF providing higher SNDR may be used. Finally, the trade-off between the performance improvement and hardware complexity may be tuned by appropriately selecting the values of *k* and *r*.

#### B. Manhattan vs. Euclidean Distance Comparison

As stated in previous sections, the use of Manhattan distance results in lower complexity quantizer implementations in comparison with using Euclidean distance at minimal performance and stability cost. This behavior is typical and is illustrated in Table III, where the SNDR of the MSLA modulators using Manhattan and Euclidean distances are compared. NTF 2 is chosen with various values of k, r and sinusoidal input amplitude A. The input is  $x_n = A \sin (2\pi \cdot 0.0041482n)$  and OSR = 32.

The conclusion is that choosing Manhattan distance over Euclidean usually has a minor SNDR impact of 1-2 dB. The differences become more pronounced when the input amplitude is close to the stability limit. In this marginal

TABLE III SNDR Comparison of Manhattan and Euclidean Distances

| k | r | A   | SNDR (dB) |           |  |

|---|---|-----|-----------|-----------|--|

| n | , |     | Manhattan | Euclidean |  |

| 6 | 6 | 0.5 | 69.73     | 71.96     |  |

| 6 | 6 | 0.7 | 71.45     | 71.98     |  |

| 6 | 6 | 0.9 | 60.74     | 61.44     |  |

| 6 | 4 | 0.5 | 58.28     | 58.17     |  |

| 6 | 4 | 0.7 | 62.81     | 62.17     |  |

| 6 | 4 | 0.9 | 53.39     | 58.52     |  |

| 2 | 2 | 0.5 | 67.95     | 69.86     |  |

| 2 | 2 | 0.7 | 70.41     | 71.48     |  |

| 2 | 2 | 0.9 | 65.63     | Unstable  |  |

case, Manhattan distance might offer increased stability as it is evident in the last row of Table III, i.e., the MSLA modulator employing Euclidean distance is unstable whereas the Manhattan distance one maintains stability.

#### C. Comparison With Other Look-Ahead Algorithms

The benefits of using look-ahead techniques are found mainly in their increased stability characteristics, therefore allowing for higher order loop filters, higher SNDR and increased maximum input amplitudes. Other benefits include their lower THD (total harmonic distortion) and noise modulation [19]. The observed SNDR of look-ahead modulators with *the same* comparison filter (and thus NTF) as a conventional  $\Sigma$ - $\Delta$  modulator is typically 1-2 dB lower than that of a conventional one for input values in the stable range of both modulators. However, this is mitigated by exploiting the increased stability of look-ahead modulators e.g. use of a higher order NTF or a NTF with a higher out-of-band gain.

In Section III-C a complexity comparison between various look-ahead implementations and the MSLA modulator was presented, showcasing the reduced relative complexity of the MSLA modulator. Here, we compare the performance of these modulators in terms of SNDR and maximum sinusoidal input amplitude A. The results are summarized in Table IV. The simulation results of the various look-ahead implementations, i.e., pruned look-ahead, efficient trellis and pruned tree (M-algorithm), are taken from [19]. In order to have a fair comparison we have used the same conditions for our simulations. A 5th (or 3rd) order feed-forward loop filter with resonators is used with the configuration SDM2 (or SDM4) as described in Appendix B of [19]. For the SNDR calculations a -6 dB 1 KHz sine wave is used as the input and OSR = 64is assumed with a sampling frequency of 64 · 44.1 KHz. In all circumstances 10<sup>6</sup> output samples are generated. The parameters of the algorithms were chosen so that their hardware complexity is comparable. This is the reason why the number of filter output calculations (NoFC) is included in the last column of Table IV. NoFC is calculated according to Table I.

The MSLA modulator displays similar or better performance than other look-ahead algorithms for comparable complexity. More specifically, for SDM2 the MSLA modulator with r = k = 7 or higher outperforms the other implementations in terms of SNDR, while for SDM4 the

TABLE IV Comparison of Look-Ahead Algorithms

| Look-Ahead                               | SDM2 |        | SDM4 |        | NoFC |

|------------------------------------------|------|--------|------|--------|------|

| Algorithm                                | SNDR | Max. A | SNDR | Max. A | NOFC |

| Pruned LA $(N=2)$                        | 114  | 0.69   | 83   | 0.83   | 6    |

| Pruned LA $(N = 3)$                      | 114  | 0.71   | 83   | 0.85   | 14   |

| Eff. trellis $(M = 32, N = 4, L = 4096)$ | 114  | 0.74   | -    | -      | 64   |

| Pruned tree $(M = 2, L = 4096)$          | 113  | 0.68   | -    | -      | 4    |

| Pruned tree $(M = 4, L = 4096)$          | 114  | 0.74   | -    | -      | 8    |

| Pruned tree $(M = 8, L = 4096)$          | 114  | 0.78   | -    | -      | 16   |

| MSLA (r = k = 3)                         | 111  | 0.66   | 86   | 0.79   | 4    |

| MSLA (r = k = 5)                         | 113  | 0.70   | 89   | 0.81   | 6    |

| MSLA (r = k = 7)                         | 115  | 0.69   | 89   | 0.84   | 8    |

| MSLA (r = k = 11)                        | 115  | 0.73   | 90   | 0.89   | 12   |

| MSLA (r = k = 12)                        | 115  | 0.74   | 91   | 0.90   | 13   |

selection of r = k = 3 is sufficient to give the MSLA modulator the performance advantage. A value of r = k = 12is needed for the MSLA modulator in order to exhibit the same maximum stable sinusoidal amplitude as the pruned tree algorithm with M = 4 and only the pruned tree algorithm with M = 8 outperforms it, but with the cost of higher complexity.

# D. Output Power Spectra and Applications

In the following test cases MSLA modulators with Manhattan distance as the cost function are used for the reasons discussed in Section III-B.

1) Low-Pass Modulator With DC Input: A popular application of  $\Sigma$ - $\Delta$  modulators with DC input is the generation of the divider control in fractional-N frequency synthesizers. The most common structure used is the 1-1-1 MASH modulator [23]. The drawback of MASH is its multi-bit output, which complicates the design of the divider. The MSLA modulator with a simple 3rd order low-pass filter offers comparable noise shaping and stability with 1-bit output.

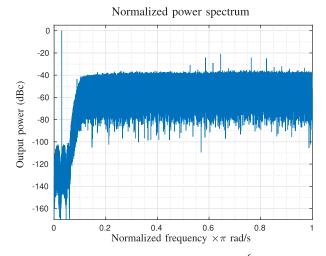

As a test-case the  $NTF = (1 - z^{-1})^3$  is used with a DC input. An advantage of this NTF is the simplicity of its coefficients, resulting in a multiplier-less, and therefore fast and power efficient, hardware implementation. The power spectrum obtained from  $2 \cdot 10^6$  output samples of the MSLA modulator with k = 2 and a DC input of 0.0025 is shown Fig. 15. There are some frequency spurs starting at  $f = 0.0025 f_s$  as it is expected from a DC input value which is a small rational fraction, namely 1/400. However, they can be eliminated when a small random dither is added to the input [24]. Simulation results also back this claim. The frequency and severity of these spurs depend on the DC input amplitude and on the modulator order. High-order modulators exhibit fewer or no spurs due to signal mixing in the higher order loop filter [1].

Fig. 15. Power spectrum relative to the carrier of  $2 \cdot 10^6$  output samples of the low-pass MSLA modulator with k = 2,  $NTF = (1 - z^{-1})^3$  and a DC input with amplitude 0.0025.

2) Low-Pass Modulator With Sinusoidal Input: The low-pass  $\Sigma$ - $\Delta$  modulator is used in a multitude of applications, with audio being a major one [25], [26]. A purely digital-to-digital  $\Sigma$ - $\Delta$  converter is used to generate the 1-bit SA-CD (Super Audio CD) bitstream from explicit PCM input data [19]. Recently, 1-bit low-pass  $\Sigma$ - $\Delta$  modulators have received attention in all-digital transmitter architectures [27]–[30].

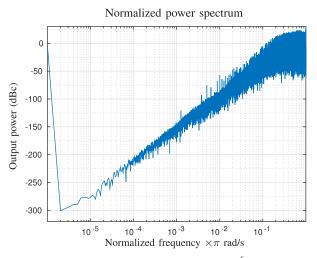

A NTF with zeros spread across the signal band, for improved in-band SNR, is chosen for the demonstration of the low-pass MSLA modulator output spectrum. The NTF is synthesized using the MATLAB Delta Sigma Toolbox [31] with the following parameters: 7-th order filter, OSR = 16, use of optimized zeros and  $NTF(\infty) = 2$ . Lee's rule states that for a conventional 1-bit high-order  $\Sigma$ - $\Delta$  modulator stability is guaranteed when  $NTF(\infty) < 1.5$  [1]. Indeed, MATLAB simulation indicates that this NTF is unstable when used in a conventional  $\Sigma$ - $\Delta$  modulator. Due to the low oversampling ratio (OSR), offering a wide fractional signal bandwidth, forcing  $NTF(\infty) < 1.5$  results in low noise attenuation in the signal band. The MSLA modulator with this NTF, r = k = 10and a sinusoidal input signal of amplitude 0.43 is stable. The output spectrum relative to the carrier of  $2 \cdot 10^6$  output samples is shown in Fig. 16. Such a wide signal bandwidth combined with such noise attenuation is probably impossible with a conventional 1-bit  $\Sigma$ - $\Delta$  modulator. To back this claim, the highest possible  $NTF(\infty)$  of a EF SDM with a NTF designed with the same parameters, is found to be  $NTF(\infty) = 1.74$ . Its SNDR is estimated at 61.5 dB, while the SNDR of the MSLA modulator with  $NTF(\infty) = 2$  is 68.7 dB.

There are some out-of-band tones at frequencies higher than  $0.25 f_s$ , but they should be easily eliminated by a subsequent decimation filter. Simulations with various input amplitudes and frequencies, as well as different loop filters support the assertion that there are no frequency spurs in the signal band when the modulator operates far from overload.

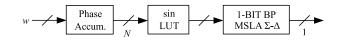

*3) Band-Pass Modulator With Sinusoidal Input:* Direct digital synthesizers use an accumulator and a sinusoidal lookup table (LUT) to generate a multi-bit digital sinewave.

Fig. 16. Power spectrum relative to the carrier of  $2 \cdot 10^6$  output samples of the wide-band low-pass MSLA modulator with r = k = 10 and a sinusoidal input with amplitude 0.43.

Fig. 17. All-digital frequency synthesis using the Multi-Step Look-Ahead band-pass modulator.

The frequency is determined by the frequency control word fed to the phase accumulator. Finally, the digital stream is converted to analog via a DAC. Multi-bit DAC non-linearities and low effective number of bits (ENOB) introduce numerous spurs. Several works have dealt with techniques to suppress the spurs [32]–[34].

Alternatively, one can use a band-pass  $\Sigma$ - $\Delta$  modulator [35] after the sinusoidal LUT for the generation of a 1-bit output with the quantization noise shaped out of the signal frequency band [36]–[41]. This is shown in Fig. 17. The NTF of this modulator should suppress the noise over a wide bandwidth to support signal generation with varying carrier frequency. MSLA modulator's bandwidth advantage is convenient. Furthermore, converting a 1-bit digital stream to analog is much less involved compared to a multi-bit one. 1-bit data conversion, apart from jitter affecting all types of DACs, is subject only to DC offset and gain errors, both harmless for the output spectrum.

In Fig. 18 the power spectrum relative to the carrier of  $2 \cdot 10^6$  output samples of the band-pass MSLA modulator with r = k = 7 is shown. A sinusoidal input with frequency  $\omega = 2\pi \cdot 0.3814$  rad/s and amplitude 0.31 was used, while the NTF was designed with the help of the MATLAB Delta Sigma Toolbox. The parameters used for the NTF were: 8-th order filter, OSR = 16, use of optimized zeros,  $NTF(\infty) = 2$  and central frequency  $\omega_0 = 2\pi \cdot 0.38$  rad/s. Again, the combination of wide signal bandwidth and in-band noise attenuation is not achievable with a conventional 1-bit  $\Sigma \cdot \Delta$  modulator. The EF SDM with a NTF designed using the same parameters is stable up to  $NTF(\infty) = 1.69$  and achieves a SNDR of 48.7 dB. The band-pass MSLA modulator with  $NTF(\infty) = 2$  exhibits a SNDR of 54.2 dB. Finally, it should be noted that there are no spurs in the whole power spectrum frequency range.

Fig. 18. Power spectrum relative to the carrier of  $2 \cdot 10^6$  output samples of the band-pass MSLA modulator with r = k = 7 and a sinusoidal input with amplitude 0.31.

Fig. 19. The  $u_{j,n}$  computation unit.

# V. HARDWARE IMPLEMENTATION ASPECTS

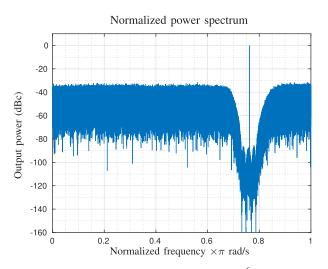

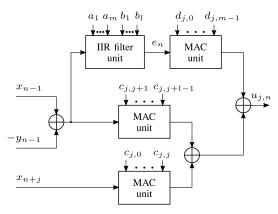

The hardware implementation of the MSLA modulator is based on the evaluation of (14), while the quantizer inputs  $u_{j,n}$ are given by (13). The hardware complexity depends on the look-ahead steps k, the quantizer's input vector length r + 1and the comparison filter.

The proposed architecture is based on a modular design, in which the MSLA modulator consists of r + 1 two-input filters  $(L_0^j, L_1^j)$ , which from now on we refer to as  $u_{j,n}$  computation units. In comparison with the brute-force approach of calculating the total cost function for each possible output sequence, as it is common in other look-ahead  $\Sigma$ - $\Delta$  architectures [19], the proposed architecture requires only one calculation of vector **u** per output symbol. This fact emphasizes the importance of the analysis presented in section III.

The block diagram of a  $u_{j,n}$  computation unit is shown in Fig. 19. This unit implements (13) and each multiply-andaccumulate (MAC) unit calculates each of the three sums involved. Moreover, the IIR filter unit computes  $e_n$  using the difference equation corresponding to (16). The quantizer can be implemented either with combinational logic (e.g. comparators) or with a ROM-based LUT. Its mapping function f is

Fig. 20. The proposed hardware architecture of the MSLA modulator with  $NTF = (1 - z^{-1})^2$ , k = 1 and r = 1.

determined by the NTF, the number of look-ahead steps k, the value of r and the choice of Manhattan or Euclidean distance. Further research is currently performed in order to determine the best implementation for the quantizer.

The topology of the loop filter implementation has an effect on the number of registers, adders and multipliers required, as well as on the total quantization noise. The most robust topologies in terms of quantization noise are the cascade and parallel forms (second-order sections), but the transposed form II implementation is more efficient in terms of required hardware [42]. Significant hardware reduction and speed improvement are possible if the loop filter and the MAC unit coefficients are powers of 2 or a sum of powers of 2. Then, all multiplications are reduced to shift operations or two shift operations and an addition.

The cascaded integrator with feedback topology seems to be the optimal structure for a hardware implementation of the loop filter as it offers the possibility to reduce the number of bits needed after each integrator while it maintains low delay [27].

# A. FPGA Implementation

As a simple test case, the hardware implementation of the MSLA modulator with  $NTF = (1 - z^{-1})^2$ , k = 1 and r = 1 is depicted in Fig. 20. Clock signals have been omitted for simplicity. The output register doubles as the delay element for the feedback signal. This modulator is very hardware efficient, since all multiplications reduce to shift and add operations. The bit width of the input and the registers has been set to 16 bits with 1 bit output. Further reduction of the bit widths along the signal path is possible following the design procedure in [27]. The top 4-input adder forms the  $u_{0,n}$  computation unit, i.e., the two-input filter  $(L_0^0, L_0^1)$ , and the bottom one the  $u_{1,n}$  computation unit, i.e., the two-input filter sare given by (18) and (19) respectively. In our test case we find

$L_0^0(z) = 1/(1-z^{-1}+z^{-2}), \ L_0^1(z) = (-2z^{-1}+z^{-2})/(1-z^{-1}+z^{-2})$  for the top filter and  $L_1^0(z) = z/(1-z^{-1}+z^{-2}), \ L_1^1(z) = (-3z^{-1}+2z^{-2})/(1-z^{-1}+z^{-2})$  for the bottom one. The quantizer logic module implements the mapping function of Fig. 10a and has two 16-bit inputs and a 1-bit output.

In order to obtain a rough estimation of hardware requirements, the modulator has been synthesized for a Xilinx Kintex-7 development board using 16-bit fixed-point representation for the modulator signals. The synthesis tool reports 7 2-input and 2 3-input 16-bit adders, 7 16-bit and 3 1-bit registers in addition to 2 2-input 16-bit multiplexers, 1 2-input 15-bit multiplexer and 1 2-input 1-bit multiplexer. That is about 1% utilization of the FPGA resources. The maximum clock frequency was reported at 330 MHz for this FPGA, but IC implementation allows for much higher clock frequencies [43].

The proposed hardware architecture is suitable for FPGA and IC CMOS implementations. The superior speed of an IC implementation is of great importance as the OSR can be increased, and thus the noise attenuation in the pass-band can be even higher. In any case, the hardware overhead of the MSLA modulator is low, which means it can be easily and cheaply incorporated in a larger mixed-signal or all-digital design. Furthermore, the 1-bit output eliminates the need for a multi-bit DAC, leading to inherently linear, all-digital designs.

#### VI. CONCLUSIONS

The MSLA modulator, which is a modification of the 1-bit EF SDM taking into account future input samples, has been introduced. It exhibits superior stability characteristics, allowing for higher input dynamic range and more aggressive NTFs resulting in higher SNDR than conventional 1-bit  $\Sigma$ - $\Delta$  modulators. Moreover, comparison of the MSLA modulator with other look-ahead algorithms highlights its performance advantage and low relative complexity, which enables real-time operation. The MSLA modulator has been analyzed mathematically and shown to be equivalent to a number of conventional  $\Sigma$ - $\Delta$  modulators in parallel, sharing a common multi-input 1-bit quantizer. The simulation results have illustrated the advantages of the MSLA modulator in a variety of applications. Finally, a hardware architecture has been proposed and a specific FPGA implementation has been presented, showing that moderate values of k and r do not impose a significant increase in hardware complexity when compared to a conventional 1-bit  $\Sigma$ - $\Delta$  modulator.

# APPENDIX A

NOTATION OVERVIEW

*G* Comparison filter transfer function.

- *b* Comparison filter numerator coefficients.

- *a* Comparison filter denominator coefficients.

- $\ell$  Comparison filter numerator order.

- *m* Comparison filter denominator order.

- *k* Number of look-ahead steps.

- r + 1 Number of partial costs involved in the calculation of the total cost.

| ( )                        | 1 1                                                                           |

|----------------------------|-------------------------------------------------------------------------------|

| { <i>y</i> }               | The MSLA modulator output sequence.                                           |

| $\{e\}$                    | Comparison filter G output sequence.                                          |

| $\{v\}$                    | The trial feedback sequence.                                                  |

| j                          | The <i>j</i> -th look-ahead sample $(k - r \le j \le k)$ .                    |

| $S_{j,n}$                  | Partial cost associated with the <i>j</i> -th                                 |

|                            | look-ahead sample at time instant <i>n</i> .                                  |

| $c_{j,i}$                  | Coefficients associated with MSLA modulator                                   |

|                            | loop filters $\left(L_{j}^{0}(z), L_{j}^{1}(z)\right)$ .                      |

| $d_{j,i}$                  | Coefficients associated with MSLA modulator                                   |

|                            | loop filters $\left(L_{j}^{0}\left(z\right),L_{j}^{1}\left(z\right)\right)$ . |

| $u_{j,n}$                  | The output of the loop filter $\left(L_0^j(z), L_1^j(z)\right)$ .             |

| u                          | $(u_{k-r,n}, u_{k-r+1,n}, \ldots, u_{k,n})$                                   |

| V                          | $(v_0, v_1, \ldots, v_k)$                                                     |

| $D\left(\mathbf{v}\right)$ | The total cost function.                                                      |

| $f(\mathbf{u})$            | The MSLA quantizer mapping function.                                          |

| $L^0_i$                    | The transfer function of the MSLA                                             |

| 5                          | modulator's <i>j</i> -th loop filter X input.                                 |

| $L^1_i$                    | The transfer function of the MSLA                                             |

| 5                          | modulator's <i>j</i> -th loop filter <i>Y</i> input.                          |

| NTF                        | The NTF of the EF SDM (Fig. 1).                                               |

| STF                        | The STF of the EF SDM (Fig. 1).                                               |

| NTF <sub>MSLA</sub>        | The NTF of the MSLA modulator.                                                |

| <b>STF</b> <sub>MSLA</sub> | The STF of the MSLA modulator.                                                |

|                            |                                                                               |

The MSLA modulator input sequence.

$\{x\}$

# APPENDIX B

This appendix demonstrates the derivation of (12) and (13) from (8). In the following analysis it is assumed that  $\ell, m > j$ . The same equations are still valid if  $\ell \le j$  or  $m \le j$  by setting  $b_i = 0$  for  $i > \ell$  and  $a_i = 0$  for i > m respectively.

The first step is to express every  $e_{n+j}$ ,  $k - r \le j \le k$  in terms of the inputs  $x_i$ , the previous outputs  $y_i$ , the previous filter *G* outputs  $e_{n-i}$ ,  $i \ge 0$  and a linear combination of  $v_0, v_1, \ldots, v_{j-1}$ . This is accomplished by application of the filter difference equation (9) for every  $e_{n+i}$ ,  $0 < i \le j$ . Using matrix notation this is written

$$\mathbf{e}_{n+1}^{n+j} = \mathbf{B}_{x} \mathbf{x}_{n+1-\ell}^{n+j-1} - \mathbf{B}_{v} \mathbf{v}_{0}^{j-1} - \mathbf{B}_{y} \mathbf{y}_{n+1-\ell}^{n-1} - \mathbf{A} \mathbf{e}_{n+1-m}^{n+j-1}$$

(28)

where the vector notation  $\mathbf{q}_{i}^{i+p} = [q_{i+p}, q_{i+p-1}, ..., q_{i}]^{\top}$  is used,  $\mathbf{v}_{0}^{j-1} = [v_{j-1}, v_{j-2}, ..., v_{0}]^{\top}$  and

$$\mathbf{B}_{v} = \begin{bmatrix} b_{1} & b_{2} & b_{3} & \cdots & b_{j} \\ 0 & b_{1} & b_{2} & \cdots & b_{j-1} \\ \vdots & \ddots & \ddots & \ddots & \vdots \\ 0 & \cdots & 0 & b_{1} & b_{2} \\ 0 & 0 & \cdots & 0 & b_{1} \end{bmatrix}$$

(29)

$$\mathbf{B}_{y} = \begin{bmatrix} b_{j+1} & b_{j+2} & \cdots & b_{\ell} & 0 & 0 & \cdots & 0 \\ b_{j} & b_{j+1} & \cdots & b_{\ell-1} & b_{\ell} & 0 & \cdots & 0 \\ \vdots & \vdots & \vdots & \vdots & \vdots & \ddots & \ddots & \vdots \\ b_{3} & b_{4} & \cdots & b_{\ell-j+2} & b_{\ell-j+3} & \cdots & b_{\ell} & 0 \\ b_{2} & b_{3} & \cdots & b_{\ell-j+1} & b_{\ell-j+2} & \cdots & b_{\ell-1} & b_{\ell} \end{bmatrix}$$

(30)

$$\mathbf{B}_{x} = \begin{bmatrix} \mathbf{B}_{v} & \mathbf{B}_{v} \end{bmatrix}$$

(31)

with  $\mathbf{B}_v$  a  $j \times j$  matrix,  $\mathbf{B}_y$  a  $j \times (\ell - 1)$  matrix and  $\mathbf{B}_x$  a  $j \times (j + \ell - 1)$  matrix. In order to solve for  $e_{n+j}$  the last term of (28) is rewritten as

$$\mathbf{A}\mathbf{e}_{n+1-m}^{n+j-1} = \mathbf{A}_1\mathbf{e}_{n+1}^{n+j} + \mathbf{A}_2\mathbf{e}_{n+1-m}^n$$

(32)

where

$$\mathbf{A}_{1} = \begin{bmatrix} 0 & a_{1} & a_{2} & \cdots & a_{j-2} & a_{j-1} \\ 0 & 0 & a_{1} & a_{2} & \cdots & a_{j-2} \\ \vdots & \vdots & \ddots & \ddots & \ddots & \vdots \\ 0 & 0 & \cdots & 0 & a_{1} & a_{2} \\ 0 & 0 & 0 & \cdots & 0 & a_{1} \\ 0 & 0 & 0 & \cdots & 0 & 0 \end{bmatrix}$$

(33)

$$\mathbf{A}_{2} = \begin{bmatrix} a_{j} & a_{j+1} \cdots & a_{m} & 0 & 0 & \cdots & 0 \\ a_{j-1} & a_{j} & \cdots & a_{m-1} & a_{m} & 0 & \cdots & 0 \\ \vdots & \vdots & \vdots & \vdots & \vdots & \ddots & \ddots & \vdots \\ a_{2} & a_{3} & \cdots & a_{m-j+2} & a_{m-j+3} & \cdots & a_{m} & 0 \\ a_{1} & a_{2} & \cdots & a_{m-j+1} & a_{m-j+2} & \cdots & a_{m-1} & a_{m} \end{bmatrix}$$

(34)

with  $\mathbf{A}_1$  a  $j \times j$  matrix and  $\mathbf{A}_2$  a  $j \times m$  matrix. Combining (28) with (32) we get

$$\mathbf{e}_{n+1}^{n+j} = (\mathbf{I} + \mathbf{A}_1)^{-1} \left( \mathbf{B}_x \mathbf{x}_{n+1-\ell}^{n+j-1} - \mathbf{B}_v \mathbf{v}_0^{j-1} - \mathbf{B}_y \mathbf{y}_{n+1-\ell}^{n-1} - \mathbf{A}_2 \mathbf{e}_{n+1-m}^n \right).$$

(35)

Matrix  $I + A_1$  is upper unitriangular Toeplitz [44]. Its inverse is also upper unitriangular Toeplitz, i.e.

$$\mathbf{M} \triangleq (\mathbf{I} + \mathbf{A}_{1})^{-1} = \begin{bmatrix} 1 & \beta_{1} & \beta_{2} & \cdots & \beta_{j-2} & \beta_{j-1} \\ 0 & 1 & \beta_{1} & \beta_{2} & \cdots & \beta_{j-2} \\ \vdots & \ddots & \ddots & \ddots & \ddots & \vdots \\ 0 & \cdots & 0 & 1 & \beta_{1} & \beta_{2} \\ 0 & 0 & \cdots & 0 & 1 & \beta_{1} \\ 0 & 0 & 0 & \cdots & 0 & 1 \end{bmatrix}$$

(36)

where  $\beta_1 = -a_1$  and

$$\beta_{i} = -a_{i} - \sum_{p=1}^{i-1} a_{i-p} \beta_{p}$$

(37)

for  $2 \le i \le j - 1$ . Therefore  $e_{n+j}$  is derived from the first row of (35) which is written as

$$e_{n+j} = \boldsymbol{\beta}_{j-1}^{0 \top} \left[ \mathbf{B}_{v} \left( \mathbf{x}_{n}^{n+j-1} - \mathbf{v}_{0}^{j-1} \right) + \mathbf{B}_{y} \left( \mathbf{x}_{n+1-l}^{n-1} - \mathbf{y}_{n+1-l}^{n-1} \right) - \mathbf{A}_{2} \mathbf{e}_{n+1-m}^{n} \right]$$

(38)

where  $\boldsymbol{\beta}_{j-1}^{0 \top} = [\beta_0, \beta_1, ..., \beta_{j-1}]$  is a row vector with  $\beta_0 \equiv 1$ . In (38) we used  $\mathbf{B}_x = [\mathbf{B}_v \ \mathbf{B}_y]$ . Performing the matrix multiplications gives

$$e_{n+j} = \sum_{i=1}^{j} c_{j,i} \left( x_{n+j-i} - v_{j-i} \right) + \sum_{i=j+1}^{j+\ell-1} c_{j,i} \left( x_{n+j-i} - y_{n+j-i} \right) + \sum_{i=0}^{m-1} d_{j,i} e_{n-i}$$

(39)

where coefficients  $c_{j,i}$ ,  $1 \le i \le j + \ell - 1$  form the elements of row vector  $\boldsymbol{\beta}_{j-1}^{0 \top} \mathbf{B}_x$  and coefficients  $d_{j,i}$ ,  $0 \le i \le m - 1$ form the elements of row vector  $-\boldsymbol{\beta}_{j-1}^{0 \top} \mathbf{A}_2$ . Defining  $\beta_i = 0$ for  $i \ge j$  is convenient for writing them explicitly as

$$c_{j,i} = \begin{cases} \sum_{p=1}^{i} \beta_{i-p} b_p, & 1 \le i \le \ell \\ \sum_{p=1}^{\ell} \beta_{i-p} b_p, & \ell < i \le j + \ell - 1 \end{cases}$$

(40)

and

$$d_{j,i} = \begin{cases} -\sum_{p=0}^{j-1} \beta_p a_{i+j-p}, & 0 \le i \le m-j \\ -\sum_{p=0}^{m-i-1} \beta_{p+i+j-m} a_{m-p}, & m-j < i \le m-1. \end{cases}$$

(41)

In addition, we define for all  $j c_{j,0} = 1$ . The substitution of  $e_{n+j}$  as given by (39) into (10) yields the equivalent expression of  $S_{j,n}(v_0, v_1, ..., v_j)$  given in (12).

# ACKNOWLEDGEMENT

The authors would like to thank the Editor-in-Chief, the Associate Editor, and the anonymous reviewers for their valuable comments and constructive feedback.

#### REFERENCES

- R. Schreier and G. C. Temes, Understanding Delta-Sigma Data Converters, S. V. Kartalopoulos, Ed. New York, NY, USA: Wiley, 2005.

- [2] K. Hosseini and M. P. Kennedy, "Maximum sequence length MASH digital delta-sigma modulators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 54, no. 12, pp. 2628–2638, Dec. 2007.

- [3] R. F. Cordeiro, A. S. R. Oliveira, J. Vieira, and N. V. Silva, "Gigasample time-interleaved delta-sigma modulator for FPGA-based all-digital transmitters," in *Proc. IEEE 17th Euromicro Conf. Digit. Syst. Des. (DSD)*, Aug. 2014, pp. 222–227.

- [4] M. Helaoui, S. Hatami, R. Negra, and F. M. Ghannouchi, "A novel architecture of delta-sigma modulator enabling all-digital multiband multistandard RF transmitters design," *IEEE Trans. Circuits Syst. II, Express Briefs*, vol. 55, no. 11, pp. 1129–1133, Nov. 2008.

- [5] R. B. Staszewski, "State-of-the-art and future directions of highperformance all-digital frequency synthesis in nanometer CMOS," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 58, no. 7, pp. 1497–1510, Jul. 2011.

- [6] Y. L. Tang, J. G. Ma, and F. Xiong, "Implementation of sigma delta modulator for fractional-N frequency synthesis," in Proc. *Proc. IEEE Int. Symp. Integr. Circuits*, Sep. 2007, pp. 497–499.

[7] R. B. Staszewski and P. T. Balsara, "Phase-domain all-digital

- [7] R. B. Staszewski and P. T. Balsara, "Phase-domain all-digital phase-locked loop," *IEEE Trans. Circuits Syst. II, Express Briefs*, vol. 52, no. 3, pp. 159–163, Mar. 2005.

- [8] G. I. Bourdopoulos, A. Pnevmatikakis, V. Anastassopoulos, and T. L. Deliyannis, *Delta-Sigma Modulators: Modeling, Design and Applications.* London, U.K.: Imperial College Press, 2003.

- [9] P. Kiss, J. Arias, D. Li, and V. Boccuzzi, "Stable high-order delta-sigma digital-to-analog converters," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 51, no. 1, pp. 200–205, Jan. 2004.

- [10] V. Mladenov, H. Hegt, and A. van Roermund, "Stability analysis of high order sigma-delta modulators," in *Proc. Eur. Conf. Circuit Theory Design (ECCTD)*, Espoo, Finland, Aug. 2001, pp. 313–316.

- [11] S. Hein and A. Zakhor, "On the stability of sigma delta modulators," *IEEE Trans. Signal Process.*, vol. 41, no. 7, pp. 2322–2348, Jul. 1993.

- [12] S. H. Ardalan and J. J. Paulos, "An analysis of nonlinear behavior in delta-sigma modulators," *IEEE Trans. Circuits Syst.*, vol. 34, no. 6, pp. 593–603, Jun. 1987.

- [13] L. Risbo, "Sigma-delta modulators-stability analysis and optimization," Ph.D. dissertation, Tech. Univ. Denmark, Lyngby, Denmark, Jun. 1994. [Online]. Available: http://orbit.dtu.dk/services/downloadRegister/ 5274022/Binder1.pdf

- [14] A. K. Gupta and O. M. Collins, "Viterbi decoding and sigma-delta modulation," in *Proc. IEEE Int. Symp. Inf. Theory*, Lausanne, Switzerland, Jun./Jul. 2002, p. 292.

- [15] A. K. Gupta and O. M. Collins, "A new interpretation and extension of sigma delta modulation," in *Proc. IEEE Int. Symp. Inf. Theory*, Washington, DC, USA, Jun. 2001, p. 194.

- [16] R. Gopalan and O. M. Collins, "On an optimum algorithm for waveform synthesis and its applications to digital transmitters," in Proc. *Proc. IEEE Wireless Commun. Netw. Conf. (WCNC)*, Mar. 2005, pp. 1108–1113.

- [17] R. Gopalan and O. M. Collins, "An optimization approach to single-bit quantization," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 56, no. 12, pp. 2655–2668, Dec. 2009.

- [18] A. Okabe, B. Boots, K. Sugihara, and S. N. Chiu, *Spatial Tessellations: Concepts and Applications of Voronoi Diagrams*, 2nd ed. New York, NY, USA: Wiley, 2000.

- [19] E. Janssen and A. van Roermund, Look-Ahead Based Sigma-Delta Modulation. New York, NY, USA: Springer 2011.

- [20] J. Venkataraman and O. Collins, "An all-digital transmitter with a 1-bit DAC," *IEEE Trans. Commun.*, vol. 55, no. 10, pp. 1951–1962, Oct. 2007.

- [21] R. Schreier, "An empirical study of high-order single-bit delta-sigma modulators," *IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process.*, vol. 40, no. 8, pp. 461–466, Aug. 1993.

- [22] S. R. Norsworthy, R. Schreier, and G. C. Temes, Eds., *Delta-Sigma Data Converters: Theory, Design, and Simulation*. Piscataway, NJ, USA: IEEE Press, 1997.

- [23] K. Hosseini and M. P. Kennedy, "Mathematical analysis of digital MASH delta-sigma modulators for fractional-n frequency synthesis," Ph.D. dissertation, Res. Microelectron. Electron., 2006, pp. 309–312.

- [24] W. Chou and R. M. Gray, "Dithering and its effects on sigma-delta and multistage sigma-delta modulation," *IEEE Trans. Inf. Theory*, vol. 37, no. 3, pp. 500–513, May 1991.

- [25] E. Dallago, G. De Leo, and G. Sassone, "A current-mode power sigmadelta modulator for audio applications," *IEEE Trans. Ind. Electron.*, vol. 52, no. 1, pp. 236–242, Feb. 2005.

- [26] S. Rabii and B. A. Wooley, "A 1.8-V digital-audio sigma-delta modulator in 0.8-μm CMOS," *IEEE J. Solid-State Circuits*, vol. 32, no. 6, pp. 783–796, Jun. 1997.

- [27] R. Huang, N. Lotze, and Y. Manoli, "On design a high speed sigma delta DAC modulator for a digital communication transceiver on chip," in *Proc. IEEE 11th Euromicro Conf. Digit. Syst. Design Archit., Methods Tools*, 2008, pp. 53–60.

- [28] A. Frappe, A. Flament, B. Stefanelli, A. Kaiser, and A. Cathelin, "An all-digital RF signal generator using high-speed ΔΣ modulators," *IEEE J. Solid-State Circuits*, vol. 44, no. 10, pp. 2722–2732, Oct. 2009.

- [29] N. V. Silva, A. S. R. Oliveira, U. Gustavsson, and N. B. Carvalho, "A dynamically reconfigurable architecture enabling all-digital transmission for cognitive radios," in *Proc. IEEE Radio Wireless Symp. (RWS)*, Jan. 2012, pp. 1–4.

- [30] C. Basetas and P. P. Sotiriadis, "Single-bit-output all-digital frequency synthesis using multi-step look-ahead bandpass  $\Sigma \Delta$  modulator-like quantization processing," in *Proc. IEEE Int. Freq. Control Symp. Eur. Freq. Time Forum*, Denver, CO, USA, Apr. 2015, pp. 448–451.

- [31] R. Schreier. (Dec. 2011). Delta Sigma Toolbox. [Online]. Available: http://www.mathworks.com/matlabcentral/fileexchange/19-delta-sigmatoolbox

- [32] P. P. Sotiriadis and K. Galanopoulos, "Direct all-digital frequency synthesis techniques, spurs suppression, and deterministic jitter correction," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 59, no. 5, pp. 958–968, May 2012.

- [33] J. Vankka, "Spur reduction techniques in sine output direct digital synthesis," in *Proc. IEEE Int. Freq. Control Symp.*, Honolulu, HI, USA, Jun. 1996, pp. 951–959.

- [34] V. S. Reinhardt, "Spur reduction techniques in direct digital synthesizers," in *Proc. IEEE Int. Freq. Control Symp.*, Salt Lake City, UT, USA, Jun. 1993, pp. 230–241.

- [35] R. Schreier, "Noise-shaped coding," Ph.D. dissertation, Univ. Toronto, Toronto, ON, Canada, 1991.

- [36] K. Galanopoulos, C. Basetas, and P. P. Sotiriadis, "Delta-sigma modulation techniques to reduce noise and spurs in all-digital RF transmitters," in *Proc. IEEE Int. Freq. Control Symp.*, Taipei, Taiwan, May 2014, pp. 1–3.

- [37] R. Schreier and M. Snelgrove, "Bandpass sigma-delta modulation," *Electron. Lett.*, vol. 25, no. 23, pp. 1560–1561, Nov. 1989.

- [38] J. Sommarek, J. Vankka, J. Ketola, J. Lindeberg, and K. Halonen, "A digital modulator with bandpass delta-sigma modulator," in *Proc.* 30th Eur. Solid-State Circuits Conf., Sep. 2004, pp. 159–162.