# An Analog, Low-Power Threshold Classifier tested on a Bank Note Authentication Dataset

Vassilis Alimisis, Georgios Gennis, Errikos Tsouvalas, Christos Dimas and Paul P. Sotiriadis

Department of Electrical and Computer Engineering

National Technical University of Athens, Greece

E-mail: alimisisv@gmail.com, giorgosyennis@gmail.com, erricostsouvalas@gmail.com, chdim@central.ntua.gr, pps@ieee.org

Abstract—Bank note authentication devices are used widely in many large scale stores and companies. Their main focus is to accurately detect all the forged bank notes regardless of a few false alarms on genuine ones. In this work, a low power (210nW), area efficient  $(0.057mm^2)$ , analog threshold classifier is proposed to operate as a bank note authentication circuit. The architecture consists of bump and Winner-Take-All circuits. A real-world bank note authentication dataset is used to confirm the proper operation of the proposed classifier, via post-layout simulations in a TSMC 90nm CMOS process, using the Cadence IC Suite. The achieved recall (91.0%) indicates that the classifier is capable of detecting forged bank notes successfully.

Index Terms—Analog VLSI implementation, Area-Efficiency, Bank Note Authentication, Low-Power design, Threshold Classifier

## I. INTRODUCTION

Internet of things (IoT) devices capture and create various forms of sensor data such as images and videos. All these devices can be used in a variety of applications which contain information on all aspects of human production and life [1]. Using machine learning (ML) in live applications such as real-time image recognition requires flexible systems and a lot of model training. A rising research topic in IoT domain is Computer Vision, in which information is extracted from images and videos [2]. Machines are able to use computer vision technologies in combination with sensors or actuators and a high accurate software to achieve image recognition. In practice, one or more concepts in an image are recognised by a trained neural network.

Various ML algorithms, offering different accuracy and complexity, have been proposed to tackle the challenges of image classification [2]. Since most image recognition techniques are constrained in terms of processing power, latency and resources, new computing paradigms are necessary. A promising solution is edge computing which pushes processing capabilities closer to the sensor [3]. This solution is critical in applications in which real-time measurements are necessary such as autonomous vehicles, surgical devices, obstacle detection etc [4]. However, this solution reduce the data transfering (minimizing the energy needed for data transferring), but it can consume a high amount of energy.

All these related applications are in many cases implemented by battery and area depended devices [5]. Combining edge [3] and analog computing [6] is an alternative solution since the information processing is based on physical laws with area efficient circuits. This combined with sub-threshold techniques results in more power efficient systems [7]. Given the need for area and power efficient devices and motivated by their increased computation requirements, we propose an analog integrated, low-power, area efficient threshold classifier for general purpose banknote authetication applications. The classifier is designed in TSMC 90nm CMOS process and tested in a real-world banknote authetication dataset [8], compared with a software based implementation.

The remainder of this paper is organized as follows. The mathematcial background regarding the proposed analog integrated threshold classifier are explained in Section II. In Section III, the main building blocks and the proposed architecture are presented. A real-world banknote authetication dataset is used to confirm the proper operation of the proposed classifier in Section IV. A comparison between hardware and software implementation and sensitivity tests are also provided. Some concluding remarks are given in Section V.

#### II. THRESHOLD CLASSIFIER

A threshold classifier is a simplified version of a Support Vector Machine [9]. In practice, it utilizes a multivariate nonlinear transformation (f()) to render two, previously intertwined, classes as linearly or almost linearly separable. Then, by tuning a threshold value  $(I_{th})$ , it manages to distinguish them as shown in:

$$y = \begin{cases} 1 & \text{if } f(X) \ge I_{th} \\ 2 & \text{if } f(X) < I_{th} \end{cases}$$

$$(1)$$

where y is the prediction of the classifier and X is a given input vector. This simple architecture is preferable in hardware implementations since it minimizes chip area in the cost classification accuracy.

In our implementation, f() is chosen to be a sum of multivariate Gaussian function, given by:

$$f(X) = \sum_{k=1}^{K} \frac{1}{\sqrt{2\pi\sigma_k}} e^{\frac{(X-M_k)^2}{\Sigma_k^2}}.$$

(2)

Here, K is the number of the selected Guassian functions,  $M_k$  and  $\Sigma_k$  are the mean value and covariance matrices of the k-th Gaussian, respectively. The Gaussian function is preferred over other alternatives due to its ease of implementation.

## **III. PROPOSED ARCHITECTURE**

The topology of the analog threshold classifier along with its basic building blocks is presented in this Section. In particular, the multivariate Gaussian functions are implemented using a multivariate Bump circuit [10]. The comparison with the threshold value is accomplished using a Winner-Take-All circuit [11]. The entire classifier operates with the supply voltage set to  $V_{DD} = -V_{SS} = 0.3V$  and all transistors are biased in the sub-threshold region.

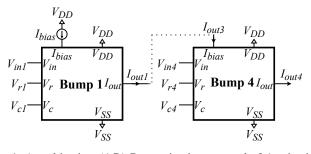

Fig. 1: A multivariate (4-D) Bump circuit composed of 4 univariate Bump circuits connected sequentially. The output of each Bump circuit is used as a bias current for the next one. The output of the last Bump circuit corresponds to the produced Gaussian curve.

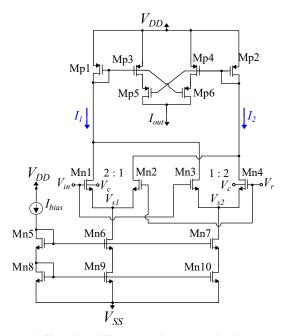

Multivariate Bump circuits produce a multivariate Gaussian function in which the mean value matrix is electronically tuned. In some architectures a diagonal covariance matrix can also be altered, affecting the width of the Gaussian function. In this work, the topology implementing a 4-D Gaussian function is presented in Fig. 1. It is composed of 4 identical univariate Bump circuits, connected in a cascaded form [10]. Each Bump circuit, shown in Fig. 2, is fully electronically tuned and therefore the multivariate one is also fully tuned. This allows for full control over the non-linear transformation function in eq. 2. The transistors' dimensions for one Bump circuit are summarized in I.

TABLE I: MOS Transistors' Dimensions (Fig. 2).

| NMOS                                  | W/L<br>(μm/μm)       | PMOS              | W/L<br>(μm/μm) |

|---------------------------------------|----------------------|-------------------|----------------|

| $M_{n1}, M_{n4}$                      | 1.6/0.4              | $M_{p1}, M_{p2}$  | 1.6/1.6        |

| $M_{n2}, M_{n3}$<br>$M_{n5} - M_{n8}$ | $0.8/0.4 \\ 0.4/1.6$ | $M_{p3} - M_{p6}$ | 0.4/1.6        |

| $M_{n9}, M_{n10}$                     | 1.6/1.6              | -                 | -              |

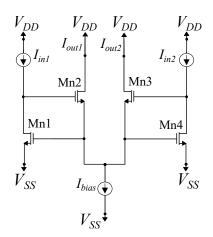

The utilized WTA circuit indicates the index of its largest input, hence performing the argmax operator. In the case of a 2-input WTA circuit, shown in Fig. 3, its operation is similar to a comparator. Specifically, by biasing its second input with a constant (threshold) current, the WTA circuit is equivalent to a current-mode comparator. This block is crucial to a threshold classifier, since it is responsible for extracting the classifier's prediction. All transistors' dimensions are set as  $W/L = 0.4 \mu m/1.6 \mu m$ .

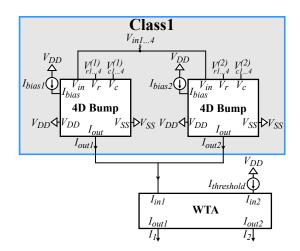

The proposed threshold classifier, presented in Fig. 4, uses a sum of k = 2 Gaussian functions for the non-linear transformation. This is implemented using 2 multivariate Bump

Fig. 2: A differential difference pair Bump circuit. The voltage parameters  $V_r$  and  $V_c$  and the bias current  $I_{bias}$  control the mean value, the variance and the height of the produced Gaussian curve  $(I_{out})$ , respectively.

Fig. 3: A WTA circuit with 2 inputs and 2 outputs. Its operation is similar to a current-mode comparator.

circuits and then simply adding their output currents. This summation is then compared to the threshold current  $I_{threshold}$  and the classifier's prediction is in fact the WTA's first output current ( $I_1$ ). This current is in a binary format; a logical 1 (a high current value) indicates the first class as the winning one and a logical 0 (a low current value) the second one. This design is easily scalable for any number of Gaussians and/or dimensions.

#### IV. BANK NOTE AUTHENTICATION DATASET

To test the threshold classifier, a real-world bank note authentication dataset was used [8]. The data include genuine and forged bank notes from the University of Applied Sciences,

Fig. 4: The proposed threshold classifier. It is comprised of 2 multivariate Bump circuits, performing the non-linear transformation, and 1 WTA circuit acting as a current-mode comparator. The  $I_{threshold}$ controls the decision boundary of the classifier.

Ostwestfalen-Lippe. They are recorded using a simple camera and 4 image related features are extracted and used to train a software-based model, which is identical to the analog one. This model's parameters are then imported to the analog circuit for its validation. On the following, two tests, validating the classifier's accuracy and the circuit's stability, are presented. Both of them are conducted on the layout presented in Fig.5.

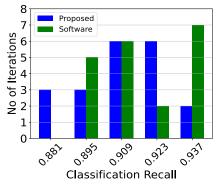

First, the hardware implementation is compared to the aforementioned software one. Since identifying all the forged banknotes is of vital importance, the comparison is also based on the classifiers recall, given by:

$$recall = \frac{Identified FBN}{Identified FBN + Unidentified FBN}, \quad (3)$$

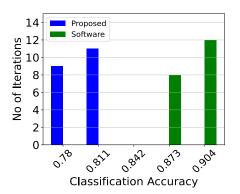

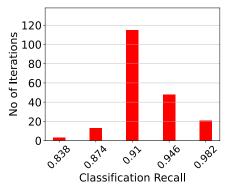

where, FBN stands for Forged Bank Notes [12]. To account for the experiment's randomness, the results from 20 different training-test iterations are presented in Figs. 6 and 7. The circuit's sensitivity is confirmed via a Monte Carlo analysis on its layout. In particular, Fig. 8 corresponds to the Monte Carlo Histogram for N = 200 points. The results for both tests are also summarized in Table II.

Fig. 5: The layout of the implemented classifier

#### V. ANALOG CLASSIFIERS SUMMARY AND DISCUSSION

In Table III, a performance summary that includes both model and circuit related parameters is presented. Using Bump

Fig. 6: Comparison between hardware (post-layout simulation) and software implementations over 20 iterations for the proposed classifier, regarding the classification recall.

Fig. 7: Comparison between hardware (post-layout simulation) and software implementations over 20 iterations for the proposed classifier, regarding the classification accuracy.

TABLE II: Performance Results for the 2 conducted tests.

| Method               | Best  | Worst | Mean  | Std.  |

|----------------------|-------|-------|-------|-------|

| Software (recall)    | 0.944 | 0.893 | 0.919 | 0.017 |

| Proposed (recall)    | 0.940 | 0.874 | 0.910 | 0.017 |

| Software (accuracy)  | 0.920 | 0.864 | 0.894 | 0.013 |

| Proposed (accuracy)  | 0.823 | 0.765 | 0.795 | 0.015 |

| Monte Carlo (recall) | 1.000 | 0.820 | 0.922 | 0.027 |

Fig. 8: Post-layout Monte Carlo sensitivity analysis histogram for N = 200 points, regarding the classifier's recall score.

circuits as their main building block, a Gaussian Mixture Model (GMM)-based classifier [13], Support Vector Machines

| Area           | Energy per classification                                | Power<br>Consumption | No. of<br>dimensions | Classifier | Technology  |              |

|----------------|----------------------------------------------------------|----------------------|----------------------|------------|-------------|--------------|

| $0.057mm^{2}$  | $\frac{2.5 \text{ pJ}}{\text{classification}}$           | 210nW                | 4                    | Threshold  | 90nm        | This<br>work |

| $0.451 mm^2$   | $\frac{96 \text{ pJ}}{\text{classification}}$            | $12.0 \mu W$         | *16                  | GMM        | 90nm        | [13]         |

| $9.000 mm^{2}$ | $\frac{460 \text{ pJ}}{\text{sample}}$                   | 5.9mW                | N/A                  | SVM        | $0.5 \mu m$ | [14]         |

| $0.060mm^{2}$  | $\frac{252 \text{ pJ}}{\text{vector}}$                   | $220.0 \mu W$        | 2                    | SVM        | 180nm       | [15]         |

| $9.000mm^2$    | $\frac{21 \text{ nJ}}{\text{classification}}$            | 840.0nW              | 14                   | SVM        | $0.5 \mu m$ | [16]         |

| $0.030mm^{2}$  | $\frac{2.15 \text{ pJ}}{\text{classification}}$          | 365nW                | 5                    | Bayesian   | 90nm        | [17]         |

| $0.050mm^2$    | $\frac{0.66 \sim 3.1 \text{ pJ}}{\text{classification}}$ | $112\sim 520 nW$     | 7                    | GRBFN      | 90nm        | [18]         |

| $0.951 mm^{2}$ | N/A                                                      | $1.53 \mu W$         | 2                    | K-means    | 180nm       | [19]         |

| $9.990mm^{2}$  | N/A                                                      | 460.3mW              | 16X16                | LSTM       | 180nm       | [20]         |

TABLE III: Analog ML Algorithm Summary. \* No. of dimensions designed on the layout.

(SVM) [14]–[16], a Bayesian classifier [17], a Gaussian Radial Basis Function Network (GRBFN) [18], a K-meansbased classifier [19] and a Long Short-Term Memory network (LSTM) [20] have been proposed in literature. The main criteria for selecting a specific model/network is the tradeoff between accuracy and system complexity or resources. In this work, we focus on the power and area efficiency, while maintaining a reasonable accuracy. To this end, we proposed a low-power (210 nW), area efficient (0.057 $mm^2$ ), analog threshold classifier.

### VI. CONCLUSION

An analog integrated, low power, area efficient threshold classifier was proposed in this work. Its main building blocks are bump circuits along with a current-mode comparator (WTA circuit). A real-world bank note authentication dataset was used to validate the classifier's performance. All post-layout simulation results are conducted in a TSMC 90nm CMOS process and are compared with a software-based implementation. Its sufficient recall allows for its operation as either a stand alone device or a wake up circuitry, when a need for higher security is required.

#### REFERENCES

- A. Taivalsaari and T. Mikkonen, "On the development of iot systems," in 2018 Third International Conference on Fog and Mobile Edge Computing (FMEC). IEEE, 2018, pp. 13–19.

- [2] I. Aydin and N. A. Othman, "A new iot combined face detection of people by using computer vision for security application," in 2017 International Artificial Intelligence and Data Processing Symposium (IDAP). IEEE, 2017, pp. 1–6.

- [3] W. Shi and S. Dustdar, "The promise of edge computing," *Computer*, vol. 49, no. 5, pp. 78–81, 2016.

- [4] J. Pan and J. McElhannon, "Future edge cloud and edge computing for internet of things applications," *IEEE Internet of Things Journal*, vol. 5, no. 1, pp. 439–449, 2017.

- [5] J. Henkel, S. Pagani, H. Amrouch, L. Bauer, and F. Samie, "Ultralow power and dependability for iot devices (invited paper for iot technologies)," in *Design, Automation & Test in Europe Conference & Exhibition (DATE), 2017.* IEEE, 2017, pp. 954–959.

- [6] W. Haensch, T. Gokmen, and R. Puri, "The next generation of deep learning hardware: Analog computing," *Proceedings of the IEEE*, vol. 107, no. 1, pp. 108–122, 2018.

- [7] A. Wang, B. H. Calhoun, and A. P. Chandrakasan, Sub-threshold design for ultra low-power systems. Springer, 2006, vol. 95.

- [8] "Bank Note Authentication Data Set, uci," https://archive.ics.uci.edu/ml/datasets/banknote+authentication, accessed: 2022-08-29.

- [9] E. Mayoraz and V. Robert, "Maximizing the robustness of a linear threshold classifier with discrete weights," *Network: Computation in Neural Systems*, vol. 5, no. 2, p. 299, 1994.

- [10] V. Alimisis, M. Gourdouparis, G. Gennis, C. Dimas, and P. P. Sotiriadis, "Analog gaussian function circuit: Architectures, operating principles and applications," *Electronics*, vol. 10, no. 20, p. 2530, 2021.

- [11] J. Lazzaro, S. Ryckebusch, M. A. Mahowald, and C. A. Mead, "Winnertake-all networks of o (n) complexity," *Advances in neural information* processing systems, vol. 1, 1988.

- [12] J. Lever, "Classification evaluation: It is important to understand both what a classification metric expresses and what it hides," *Nature meth*ods, vol. 13, no. 8, pp. 603–605, 2016.

- [13] V. Alimisis, G. Gennis, K. Touloupas, C. Dimas, M. Gourdouparis, and P. P. Sotiriadis, "Gaussian mixture model classifier analog integrated low-power implementation with applications in fault management detection," *Microelectronics Journal*, vol. 126, p. 105510, 2022.

- [14] R. Genov and G. Cauwenberghs, "Kerneltron: support vector" machine" in silicon," *IEEE Transactions on Neural Networks*, vol. 14, no. 5, pp. 1426–1434, 2003.

- [15] K. Kang and T. Shibata, "An on-chip-trainable gaussian-kernel analog support vector machine," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 57, no. 7, pp. 1513–1524, 2009.

- [16] S. Chakrabartty and G. Cauwenberghs, "Sub-microwatt analog vlsi trainable pattern classifier," *IEEE Journal of Solid-State Circuits*, vol. 42, no. 5, pp. 1169–1179, 2007.

- [17] V. Alimisis, G. Gennis, C. Dimas, and P. P. Sotiriadis, "An analog bayesian classifier implementation, for thyroid disease detection, based on a low-power, current-mode gaussian function circuit," in 2021 International Conference on Microelectronics (ICM). IEEE, 2021, pp. 153–156.

- [18] V. Alimisis, G. Gennis, C. Dimas, M. Gourdouparis, and P. P. Sotiriadis, "An ultra low power analog integrated radial basis function classifier for smart iot systems," *Analog Integrated Circuits and Signal Processing*, pp. 1–12, 2022.

- [19] A. R. Mohamed, L. Qi, and G. Wang, "A power-efficient and reconfigurable analog artificial neural network classifier," *Microelectronics journal*, vol. 111, p. 105022, 2021.

- [20] Z. Zhao, A. Srivastava, L. Peng, and Q. Chen, "Long short-term memory network design for analog computing," ACM Journal on Emerging Technologies in Computing Systems (JETC), vol. 15, no. 1, pp. 1–27, 2019.